# **Fast Charging Physical Layer IC for USB Interfaces**

TypeC PD2.0/PD3.0/PPS,QC3.0/QC2.0,FCP,SCP,AFC, Apple 2.4A, BC1.2

## 1. Features

- Support charging standards including :

- Support QC4/QC4+

- Compatible with QC2.0/QC3.0

- Support Class B

- USB PD2.0/PD3.0/PPS DFP

- SCP, FCP

- > AFC

- > MTK PE+ 1.1&2.0

- > Apple 2.4A, Samsung 2.0A and BC1.2

- Support USB PD2.0/PD3.0/PPS

- USB PD3.0 with PPS Certificate Number: TID:3135

- > Auto detect USB PD device plug in or out

- Configurable SRC\_CAP package broadcast

- Support Samsung<sup>®</sup> AFC

- Support Huawei<sup>®</sup> SCP (option)

- Support Huawei<sup>®</sup> FCP

- Support Apple 2.4A: DP=2.7V, DM=2.7V

- Support Samsung 2.0A: DP=1.2V, DM=1.2V

- Support BC1.2: DP short DM automatically

- Default 5 V mode operation

- Support NTC protection

- Support 100KHz~400KHz IIC interface

- Support DP,DM,CC1,CC2 overvoltage protection

- Support DP,DM weak short to GND protection

- VIN working voltage: 3.3V~30V

- Package: QFN24

## 2. Description

IP2723T is a fast charging Physical Layer IC dedicated for USB ports, which supports 11 kinds of fast charging standards, including USB PD2.0/PD3.0 /PPS (Programmable Power Supply), HVDCP QC2.0/QC3.0 (Quick Charge), AFC (Samsung® Adaptive Fast Charge), SCP (Hisilicon® Super Charge Protocol ) and FCP (Hisilicon® Fast Charge Protocol), MTK PE+ 1.1&2.0, Apple 2.4A, Samsung 2.0A and BC1.2.

IP2723T support automatically detecting the connected device's type and switching standards type to responding for fast charging requirements.

## 3. Typical Applications

- USB power output ports for AC adapters, Power Banka, Car chargers

- Battery chargers for smart phones, tablets, netbooks, digital cameras, and Bluetooth accessories

# 4. Typical Application Schematic

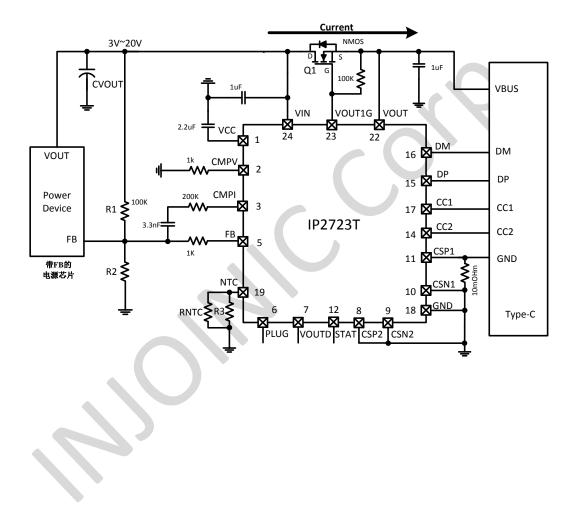

### **FB MODE**

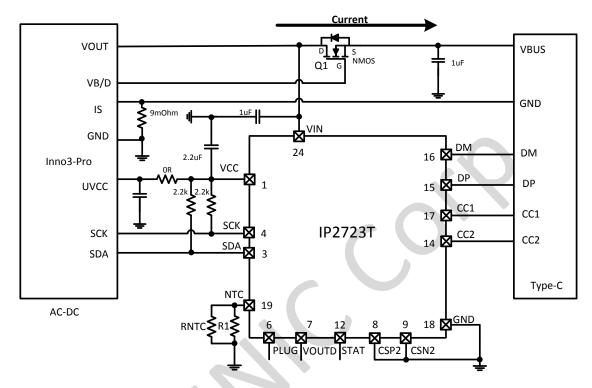

## I2C MODE

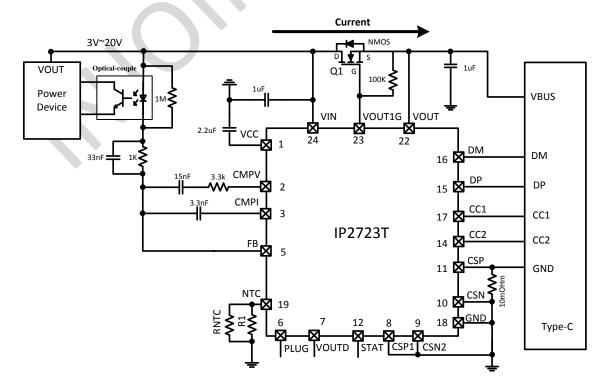

### **Optocoupler MODE**

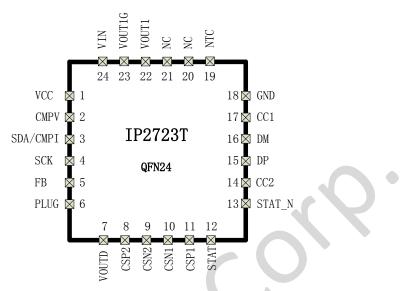

## 5. PIN Description

| Pin No. | Pin name     | Pin description                                                            |

|---------|--------------|----------------------------------------------------------------------------|

| 1       | VCC          | VCC Internal power supply output, need external 2.2 uF capacitance         |

| 2       | CMPV         | Feedback loop compensation of voltage                                      |

| 3       | CMPI/SDA     | Feedback loop compensation of current/I2C data                             |

| 4       | SCK          | I2C clock                                                                  |

| 5       | FB           | Feedback PIN. Connect to the FB line of Regulator to the power device with |

|         |              | FB control, current source/sink for voltage regulation                     |

| 6       | PLUGIN/GPIO2 | General purpose IO2                                                        |

| 7       | VOUTD/GPIO1  | Discharge Control /General purpose IO1                                     |

| 8       | CSP2         | ground                                                                     |

| 9       | CSN2         | ground                                                                     |

| 10      | CSN1         | Current sense negative PIN                                                 |

| 11      | CSP1         | Current sense positive PIN                                                 |

| 12      | STAT         | TypeC Connection Flag, Output Low Attached; Output High Detached           |

| 13      | STAT_N       | TypeC Connection Flag, Output High Attached; Output Low Detached           |

| 14      | CC2          | Type-C CC2 line                                                            |

| 15      | DP           | USB DP data line                                                           |

| 16      | DM           | USB DM data line                                                           |

| 17      | CC1          | Type-C CC1 line                                                            |

| 18      | GND          | ground                                                                     |

| 19      | NTC          | NTC Resistor input for temperature sense                                   |

| 20      | NC           | Not connect                                                                |

| 21      | NC           | Not connect                                                                |

| 22      | VOUT         | VOUT discharge pin                                                         |

| 23      | VOUTG        | VOUT output path control on the NMOS                                       |

| 24      | VIN          | Power input                                                                |

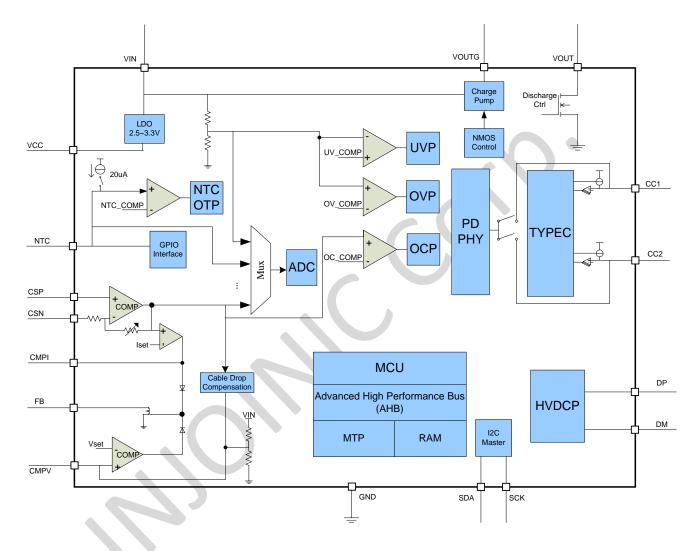

## 6. Internal Block Diagram

# 7. Absolute Maximum Ratings

| Parameters                     | Symbol                         | Value     | Unit |

|--------------------------------|--------------------------------|-----------|------|

| VIN Input Voltage Range        | VIN                            | -0.3 ~ 30 | v    |

| VOUT Input Voltage Range       | VOUT                           | -0.3 ~ 30 | V    |

| VOUTG Input Voltage Range      | VOUTG                          | -0.3 ~ 30 | v    |

| VCC Input Voltage Range        | VCC                            | -0.3 ~ 6  | V    |

| DP, DM Input Voltage Range     | $V_{\text{DP}}, V_{\text{DM}}$ | -0.3~25   | v    |

| CC1,CC2 Input Voltage Range    | $V_{CC1}, V_{CC2}$             | -0.3~30   | v    |

| Other Pins Input Voltage Range | V <sub>other</sub>             | -0.3~6    | v    |

| Junction Temperature Range     | TJ                             | -40 ~ 150 | C    |

| Storage Temperature Range      | T <sub>STG</sub>               | -60 ~ 150 | C    |

| Lead Temperature Range         | Τ <sub>s</sub>                 | 260       | C    |

| (Soldering, 10sec)               |                 |    |       |

|----------------------------------|-----------------|----|-------|

| Package Thermal Resistance       | $\theta_{A}$    | 90 | Ĉ     |

| Package Thermal Resistance       | θ <sub>JC</sub> | 39 | Ĉ     |

| Human Body Model (HBM)           | ESD             | 2  | KV    |

| Moisture Sensitivity Level (MSL) | MSL             | 3  | Level |

\*Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

Exposure to Absolute Maximum Rated conditions for extended periods may affect device reliability.

\*Voltages are referenced to GND unless otherwise noted.

## 8. Recommended Operating Conditions

| Parameter           | Symbol         | Min. | Тур. | Max. | Unit |

|---------------------|----------------|------|------|------|------|

| Input Voltage       | VIN            | 3    |      | 25   | V    |

| Ambient Temperature | T <sub>A</sub> | -40  |      | 85   | °C   |

\*Devices' performance cannot be guaranteed when working beyond those Recommended Operating Conditions.

## 9. Electrical Characteristics

Unless otherwise specified, T A =25  $^\circ\!\mathrm{C}$

| Parameter                        | Symbol              | Test Conditions                                      | Min. | Тур.  | Max. | Unit |

|----------------------------------|---------------------|------------------------------------------------------|------|-------|------|------|

| Input Voltage                    | VIN                 | Supplied directly                                    | 3    |       | 25   | V    |

| Input UVLO Threshold             | UVLO                | VIN/VCC Falling                                      | 2.5  |       | 2.9  | V    |

| Output Voltage Range             | VOUT                |                                                      | 3    |       | 21   | V    |

| Output Voltage Range Accuracy    | rianglevout         |                                                      | -3   |       | 3    | %    |

| OVP Voltage point                | V                   | VOUT=5V                                              | 6.0  | 6.2   | 6.7  | V    |

| OVP VOltage point                | V <sub>OVP</sub>    | VOUT=9V                                              | 10.8 | 11    | 11.5 | V    |

| OCP current point                | I <sub>OCP</sub>    | Rs=10mR                                              | 0.2  |       | 6.4  | А    |

| OCP current point accuracy       | $\triangle I_{OCP}$ | Rs=10mR                                              | -150 |       | +150 | mA   |

|                                  | I <sub>NOR</sub>    | No load, CC pin<br>floating, VIN=5V                  | 3    | 4     | 5    | mA   |

| Quiescent Current                | I <sub>STDBY</sub>  | MCU OFF, Standby<br>mode, CC pin<br>floating, VIN=5V | 0.6  | 1.2   | 1.4  | mA   |

| HVDCP (QC2.0&QC3.0)              |                     |                                                      |      |       |      |      |

| Data Detect Voltage<br>Threshold | $V_{DATA\_REF}$     |                                                      | 0.25 | 0.325 | 0.4  | V    |

| Output Voltage Selection<br>Reference | $V_{SEL\_REF}$                  |                       | 1.8   | 2    | 2.2  | V    |

|---------------------------------------|---------------------------------|-----------------------|-------|------|------|------|

| DP High Glitch Filter Time            | T <sub>GLITCH(BC)_DP_H</sub>    |                       | 1000  | 1250 | 1500 | ms   |

| DM Low Glitch Filter Time             | T <sub>GLITCH(BC)_DM_L</sub>    |                       | 1     | 2    | 3    | ms   |

| Output Voltage Glitch<br>Filter Time  | T <sub>GLITCH</sub> (V)_CHANGE  |                       | 20    | 40   | 60   | ms   |

| Continuous Mode Glitch<br>Filter Time | T <sub>GLITCH_CONT_CHANGE</sub> |                       | 100   |      | 200  | us   |

| DM and DP Short Resistance            | R <sub>SHORT</sub>              | V <sub>DP</sub> =0.6V | 20    | 30   | 40   | Ohm  |

| DM Pull-down Resistance               | R <sub>DM_DOWN</sub>            | V <sub>DP</sub> =0.6V | 14.25 | 20   | 24.8 | kOhm |

| DP Pull-down Resistance               | R <sub>DAT_LKG</sub>            | V <sub>DP</sub> =0.6V | 200   | 500  | 800  | kOhm |

| DCP                                   |                                 |                       |       |      |      |      |

| Samsung DP/DM Output<br>Voltage       |                                 |                       | 1.08  | 1.2  | 1.32 | v    |

| Samsung DP/DM Output<br>Impedance     |                                 |                       | 70    | 100  | 130  | kOhm |

| Apple 2.4A DP/DM Output<br>Voltage    |                                 |                       | 2.64  | 2.7  | 2.76 | v    |

| Apple 2.4A DP/DM Output<br>Impedance  |                                 |                       | 20    | 30   | 40   | kOhm |

| NTC                                   |                                 |                       | •     | •    | •    |      |

| NTC OTP Current Source                | I <sub>OTP</sub>                |                       | 19.4  | 20   | 20.6 | uA   |

| NTC OTP Voltage Threshold             | V <sub>OTP</sub>                |                       | 0.1   |      | 3    | V    |

## **10. Function Description**

### **DP/DM Quick Charge**

IP2723T can automatically detects Quick Charge 2.0/3.0 capable devices with handshake by USB D+/D- data line. It's also complaint with BC1.2.

- BC1.2: Shorting D+ Line to D- Line.

- Quick Charge 2.0/3.0: D+ and D- line configuration see **Table 1**.

#### Table 1 QC2.0/3.0 DP/DM configuration:

| DP    | DM    | Result(Class A) | Result(Class B) |

|-------|-------|-----------------|-----------------|

| 0.6 V | GND   | 5 V             | 5 V             |

| 3.3 V | 0.6 V | 9 V             | 9 V             |

| 0.6 V | 0.6 V | 12 V          | 12 V          |

|-------|-------|---------------|---------------|

| 0.6 V | 3.3 V | Continue Mode | Continue Mode |

| 3.3 V | 3.3 V | Кеер          | 20V           |

#### TYPE-C /PD

The USB Type-C connector uses CC pins for configuration including the ability for a Source to advertise to its port partner (Sink) the amount of current it can apply:

- Default values defined by the USB Specification (500 mA for USB 2.0 ports, 900 mA for USB 3.1 ports)

- 1.5A

- 3.0A

Integrated with certification standard USB Power Delivery (PD) controller

Support PD2.0/PD3.0/PPS

PDO and PPS can be configured according to customer requirements.

#### Discharge

When the output voltage is adjusted from high voltage to low voltage, especially from 20V to 5V, it requires a discharge current to fulfill the transition time specification of PD, and it cannot be greater than 285mS.

The internal 400ohm pull-down resistor is turned on, when the output voltage needs to be quickly discharged.

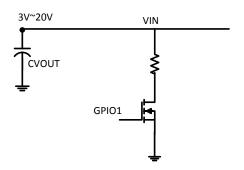

If the capacitance is relatively large and the internal bleeder is not enough, VOUTD/GPIO1 can control the external NMOS to strengthen the bleed.

The resistance value is based on the actual situation.

#### Voltage regulation mode

#### > FB Mode

IP2723T integrated FB control line used for accurate voltage regulation by source/sink current with precise 2uA/step in minimum. FB sink 40uA current for 9V output voltage; FB sink 70uA current for 12V output voltage; FB sink 150uA current for 20V output voltage; when the output voltage is default 5V, FB neither source nor sink current.

In typical applications, IP2723T FB connects to the regulator's FB line, resistor (R1) between VOUT and FB should apply 100kOhm with high precision (1%), resistor (R2) value between FB and GND should refer to the regulator adopted, resistance of R2 can be calculated by equation:

$$VFB = \frac{VOUT}{R1 + R2} * R2$$

## > Optocoupler Mode

IP2723T integrates an optocoupler driver circuit, and the FB pin is connected to the Cathode end of the optocoupler for use in isolated power supplies. The value of external compensation network capacitance, resistance of CMPV and CMPI needs to be adjusted according to the specific parameters of the front-end power network, The CMPV compensation network is used to achieve VOUT output voltage stability. The CMPI compensation network is used to achieve stability of power control.

### > I2C Mode

IP2723T integrate I2C master control interface, can cooperate with the power supply chip, such as Inno3 pro etc.

### **Cable Drop Compensation**

IP2723T integrates the line compensation function, which can increase the output voltage in a certain proportion according to the current output current to compensate for linear loss. FB mode and Optocoupler mode can be increased according to the compensation coefficients of 0mV/A, 62.5mV/A, and 125mV/A.

For example, if the compensation coefficient of 125mV/A is selected, if the no-load output voltage is 5.0V, then the actual output voltage=5.0V+3A\*125mV/A=5.375V when the output current is 3A

#### Protections

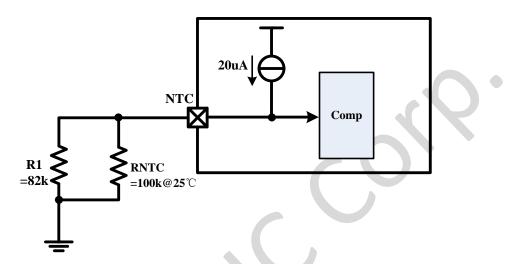

> NTC

IP2723T support NTC function used for temperature detection. NTC pin output 20uA current then detect the voltage on NTC pin to determine the present temperature.

### > OVP and UVP

IP2723T realizes over-voltage and under-voltage protection functions by detecting the voltage of VIN. The over-voltage threshold (100%~140%) and the under-voltage threshold (0~100%) can be flexibly set according to the percentage of the current output voltage. When an abnormal event of over-voltage or under-voltage occurs, the Gate will be pulled low and the external path NMOS transistor will be closed. If the abnormal event disappears, the Type-C handshake and PD communication will be re-established.

### > OTP

IP2723T integrates internal junction temperature OTP protection. Junction temperature protection occurs when the junction temperature exceeds 135  $^{\circ}$ C

### > OCP

IP2723T realizes OCP overcurrent protection by detecting the current flowing through the sampling resistor. The overcurrent threshold can be flexibly set (100%~140%). When the current reaches the over-current threshold, the over-current abnormal protection occurs, and the Gate will be pulled low, closing the external path NMOS transistor. If the abnormal event disappears, the Type-C handshake and PD communication will be re-established.

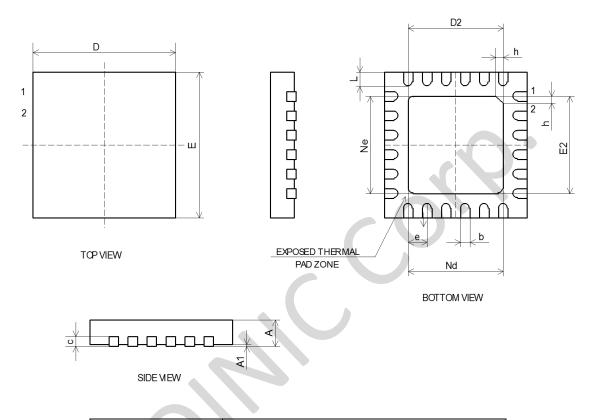

# 11.Package

| SYMDOL | MILLIMETER |         |      |  |

|--------|------------|---------|------|--|

| SYMBOL | MIN        | NOM     | MAX  |  |

| А      | 0.70       | 0.75    | 0.80 |  |

| A1     | -          | 0.02    | 0.05 |  |

| b      | 0.18       | 0.25    | 0.30 |  |

| С      | 0.18       | 0.20    | 0.25 |  |

| D      | 3.90       | 4.00    | 4.10 |  |

| D2     | 2.40       | 2.50    | 2.60 |  |

| е      |            | 0.50BSC |      |  |

| Ne     |            | 2.50BSC |      |  |

| Nd     |            | 2.50BSC |      |  |

| E      | 3.90       | 4.00    | 4.10 |  |

| E2     | 2.40       | 2.50    | 2.60 |  |

| L      | 0.35       | 0.40    | 0.45 |  |

| h      | 0.30       | 0.35    | 0.40 |  |

## **12.** Marking Specification

The top and bottom pictures of IP2723T are shown as below:

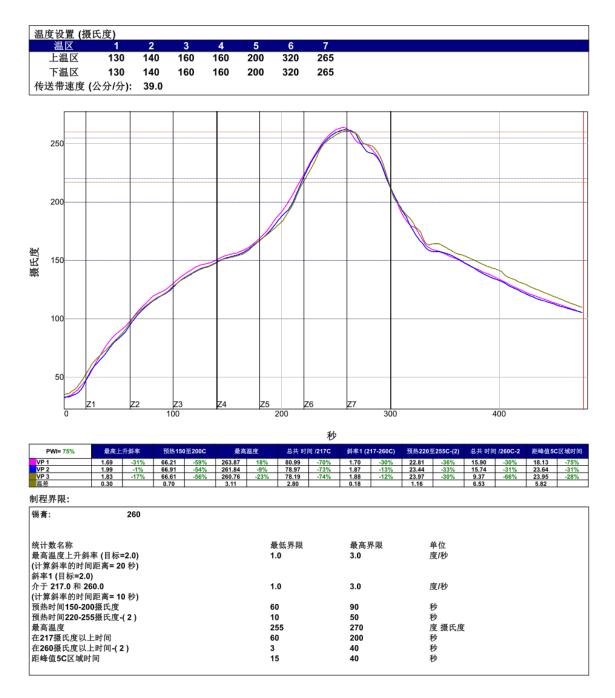

## **13.Solder Instruction**

## **14.IMPORTANT NOTICE**

INJOINIC TECHNOLOGY and its subsidiaries reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to INJOINIC TECHNOLOGY's

terms and conditions of sale supplied at the time of order acknowledgment.

INJOINIC TECHNOLOGY assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using INJOINIC TECHNOLOGY's components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of INJOINIC TECHNOLOGY's components in its applications, notwithstanding any applications-related information or support that may be provided by INJOINIC TECHNOLOGY. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify INJOINIC TECHNOLOGY and its representatives against any damages arising out of the use of any INJOINIC TECHNOLOGY's components in safety-critical applications.

Reproduction of significant portions of INJOINIC TECHNOLOGY's information in INJOINIC TECHNOLOGY's data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. INJOINIC TECHNOLOGY is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

INJOINIC TECHNOLOGY will update this document from time to time. The actual parameters of the product may vary due to different models or other items. This document voids all express and any implied warranties.

Resale of INJOINIC TECHNOLOGY's components or services with statements different from or beyond the parameters stated by INJOINIC TECHNOLOGY for that component or service voids all express and any implied warranties for the associated INJOINIC TECHNOLOGY's component or service and is an unfair and deceptive business practice. INJOINIC TECHNOLOGY is not responsible or liable for any such statements.